기계공학과 김성수 교수 연구팀:

Electronic Packaging Enhancement Engineered by Reducing the Bonding Temperature via Modified Cure Cycles - 「ACS Applied Materials & Interfaces」

우리 학교 기계공학과 김성수 교수 연구팀과 메사추세츠공과대학(MIT) 브라이언 워들(Brian L. Wardle) 교수 연구팀이 함께 반도체 패키지의 신뢰성 강화를 위한 접합 온도 제어 기반의 경화 공정을 개발하는 데 성공했다고 밝혔다. 기계공학과 박성연 박사가 제1 저자로 참여한 이번 연구는 국제 저명 학술지인 ‘ACS Applied Materials & Inter-faces’에 지난 3월 1일 게재되었다.

반도체 후공정 관심 확대

반도체 기술에는 크게 전공정과 후공정으로 나눌 수 있다. 전공정은 기판의 회로를 미세화하여 몇 나노 단위로 회로의 선폭을 줄이는 작업이라면, 후공정은 반도체 칩 여러 개를 하나로 이어주고 외부 환경으로부터 보호해 주는 반도체 패키징 기술 등을 말한다. 요즘에는 회로를 미세화하는 전공정 작업이 양자 터널링 현상으로 인해 물리적으로 불가능하게 되면서 후공정이 주목받고 있다.

휨 현상을 해결하기 위한 수정된 경화 사이클

반도체 패키지에 사용되는 EMC (Epoxy Molding Compound)는 열을 가하게 되면 화학반응이 일어나 가교결합(Cross-linking)을 하는 경화 반응(Curing reaction)이 일어난다. 따라서 다시 용융이 일어나지 않고 고온을 잘 견딜 수 있게 된다. 반도체 패키지 두께가 얇아지면 EMC를 이용하여 반도체 후공정에서 발생할 수 있는 문제점 중 하나인 휨(Warpage) 현상*이 쉽게 나타나게 되는데 연구팀은 이 해결책을 찾고자 연구를 진행하였다.

기존의 연구들은 휨 현상을 해결하기 위해서 EMC를 가공하여 기판과 EMC의 열팽창계수를 비슷하게 맞추는 실험 등을 진행했지만, 본 연구에서는 EMC와 기판 사이에 접합 온도를 예측 및 조절하여 휨 현상을 제어할 수 있는 수정된 경화 사이클을 개발하였다.

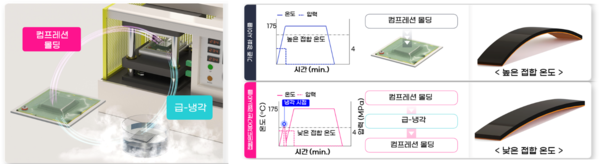

경화 사이클은 크게 기판과 EMC를 가열하는 단계, 고온 상태로 유지하는 단계, 냉각하는 단계로 이루어진다. 또한, 기판과 EMC 사이에서 EMC의 경화도가 특정 시점을 넘어가면 두 개가 접합되었다고 한다. 기존의 경화 사이클에서는 두 번째 단계에서 유지하는 온도보다 낮은 접합 온도를 가질 수 있기 때문에 연구팀은 이 사실에 착안하여 첫 번째와 두 번째 단계 사이에 급랭 구간을 만들었다.

이는 EMC의 특징 덕분에 가능했는데, 급랭해도 경화도가 유지되는 성질이 있어서 가열, 급랭 후 다시 가열을 진행하면 중간 정도의 경화도를 가지고 다시 경화를 시작해 기존의 경화 사이클보다 낮은 접합 온도를 가질 수 있게 되었다. 이 경화 사이클을 통해 기존 사이클 대비 휨은 27% 감소했고, 기판과 EMC 경계면의 접합 강도도 40% 상승했다.

새로운 변수, 경화 수축 고려

연구팀은 기존 경화 사이클을 통해 나온 결과물을 토대로 접합 온도를 정확하게 예측하는 결과도 내놓았다. 다른 논문에서는 열팽창계수를 보통 고려하여 휘어진 곡률을 측정한 후 접합 온도를 역으로 연산하는 과정을 거쳤는데 실제로는 EMC가 경화할 때 수축하는 정도에도 접합 온도에 영향을 크게 받는다는 것을 인지하여 연구팀은 이를 기반으로 정확한 접합 온도 측정 방법을 알게 되었다.

박 박사는 “반도체 후공정에 대한 연구는 다른 나라에서 몇 년 전부터 진행되어 왔지만, 한국에서는 전공정의 한계를 겪고 최근에 조명되기 시작했다”고 말했다. 그리고, "이 연구는 후공정 기술에 앞서 있는 다른 나라들을 따라잡는 연구가 될 것”이라고 밝히며, 한국의 반도체 패키징 기술에 대한 긍정적인 미래를 얘기했다.